- 您现在的位置:买卖IC网 > Sheet目录320 > DK-DEV-5AGXB3N/ES (Altera)ARRIA V DEVELOPMENT KIT

8

Available Options

AV-51001

2013.12.26

Available Options

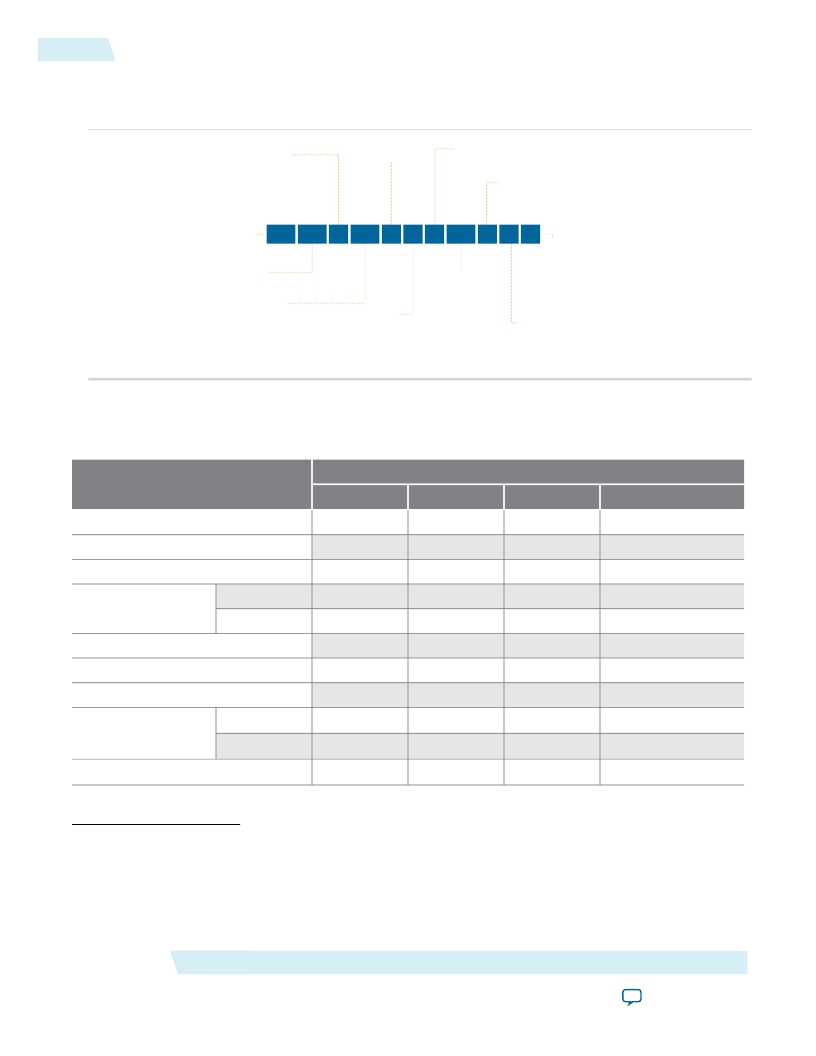

Figure 2: Sample Ordering Code and Available Options for Arria V GT Devices

Embedded Hard IPs

M : 1 hard PCIe and 2 hard

Transceiver Count

Maximum channels

D : 9

Package Type

F : FineLine BGA (FBGA)

memory controllers

G

:

18

Operating Temperature

F : 2 hard PCIe and 4 hard

memory controllers

H

K

:

:

24

36

I

: Industrial (T J = -40° C to 100° C)

Family Signature

5A : Arria V

5A

GT

F

D7

K

3

F

40

I

3

N

Optional Suffix

Indicates specific device

Family Variant

Package Code

options or shipment method

N : Lead-free packaging

GT : 10-Gbps transceivers

Member Code

C3 : 156K logic elements

C7 : 242K logic elements

D3 : 362K logic elements

D7 : 504K logic elements

Transceiver

Speed Grade

3 : 10.3125 Gbps

27 : 672 pins

31 : 896 pins

35 : 1,152 pins

40 : 1,517 pins

Contact Altera for availability

of leaded options

ES : Engineering sample

FPGA Fabric

Speed Grade

3 (fastest)

5

Maximum Resources

Table 6: Maximum Resource Counts for Arria V GT Devices

Resource

Logic Elements (LE) (K)

ALM

Register

C3

156

58,900

235,600

C7

242

91,680

366,720

Member Code

D3

362

136,880

547,520

D7

504

190,240

760,960

Memory (Kb)

M10K

MLAB

10,510

961

13,660

1,448

17,260

2,098

24,140

2,906

Variable-precision DSP Block

18 x 18 Multiplier

PLL

396

792

10

800

1,600

12

1,045

2,090

12

1,156

2,312

16

Transceiver

GPIO (6)

6 Gbps (4)

10 Gbps (5)

3 (9)

4

416

6 (24)

12

544

6 (24)

12

704

6 (36)

20

704

(4)

(5)

(6)

The 6 Gbps transceiver counts are for dedicated 6-Gbps channels. You can also configure any pair of 10 Gbps

channels as three 6 Gbps channels-the total number of 6 Gbps channels are shown in brackets.

Chip-to-chip connections only. For 10 Gbps channel usage conditions, refer to the Transceiver Architecture

in Arria V Devices chapter.

The number of GPIOs does not include transceiver I/Os. In the Quartus II software, the number of user I/Os

includes transceiver I/Os.

Altera Corporation

Arria V Device Overview

Send Feedback

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DK-DEV-5M570ZN

KIT DEV MAX V 5M570Z

DK-DEV-5SGXEA7N

KIT DEV STRATIX V FPGA 5SGXEA7

DK-DSP-2S180N

DSP PRO KIT W/SII EP2S180N

DK-DSP-3C120N

KIT DEV DSP CYCLONE III EDITION

DK-K7-CONN-CES-G

KINTEX-7 FPGA CONNECTIVITY KIT

DK-K7-EMBD-CES-G-J

KINTEX-7 FPGA EMBEDDED KIT JAPAN

DK-MAXII-1270N

KIT DEV MAXII W/EPM 1270N

DK-N2EVAL-3C25N

KIT DEV NIOS II CYCLONE III ED.

相关代理商/技术参数

DK-DEV-5ASTD5N

功能描述:KIT DEV ARRIA V FPGA 制造商:altera 系列:Arria V ST 零件状态:在售 类型:FPGA 配套使用产品/相关产品:Arria? V ST 内容:板 标准包装:1

DK-DEV-5CEA7N

功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For 5CEFA7F31C7N

RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压:

DK-DEV-5CEA7N/P

制造商:Altera Corporation 功能描述:Cyclone VE Devkit Promotional 制造商:Altera 功能描述:Cyclone VE Devkit Promotional

DK-DEV-5CEA7NES

功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For 5CEFA7F3

RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压:

DK-DEV-5CEA7NESP

制造商:Altera Corporation 功能描述:KIT DEVELOPMENT CYCLONE V E

DK-DEV-5CEA7NP

制造商:Altera Corporation 功能描述:Cyclone VE Devkit Promotional 制造商:Altera 功能描述:Cyclone VE Devkit Promotional

DK-DEV-5CGTD9N

功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For 5CGTFD9E5F35

RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压:

DK-DEV-5CGXC7NES

功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For 5CGXFC7D6F31C7N

RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: